|

FPGA,一种全新的古老计算机芯片,正在悄然改变着全球的芯片市场。知乎问题“如何评价微软在数据中心使用FPGA代替传统CPU的做法?”的下面,来自微软亚洲研究院的实习生李博杰的回答在很短的时间内就收获了近2000的点赞数。这篇文章转载自他在知乎上的回答,看看他眼中微软的FPGA布局和FPGA的研究前景吧! 问题「用 FPGA 代替 CPU」中,这个「代替」的说法不准确。我们并不是不用 CPU 了,而是用 FPGA 加速适合它的计算任务,其他任务仍然在 CPU 上完成,让 FPGA 和 CPU 协同工作。 本回答将涵盖三个问题: 1.为什么使用 FPGA,相比 CPU、GPU、ASIC(专用芯片)有什么特点? 2.微软的 FPGA 部署在哪里?FPGA 之间、FPGA 与 CPU 之间是如何通信的? 3.未来 FPGA 在云计算平台中应充当怎样的角色?仅仅是像 GPU 一样的计算加速卡吗? 一、为什么使用 FPGA? 众所周知,通用处理器(CPU)的摩尔定律已入暮年,而机器学习和 Web 服务的规模却在指数级增长。人们使用定制硬件来加速常见的计算任务,然而日新月异的行业又要求这些定制的硬件可被重新编程来执行新类型的计算任务。FPGA (Field Programmable Gate Array) 正是一种硬件可重构的体系结构,常年来被用作专用芯片(ASIC)的小批量替代品,然而近年来在微软、百度等公司的数据中心大规模部署,以同时提供强大的计算能力和足够的灵活性。

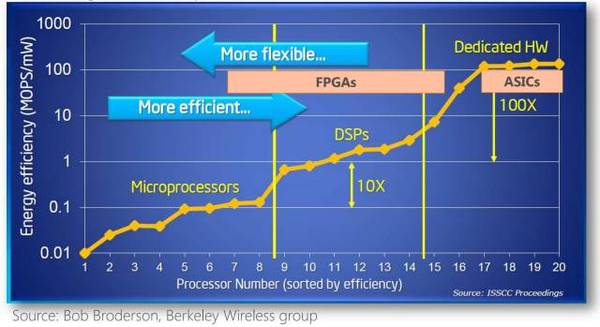

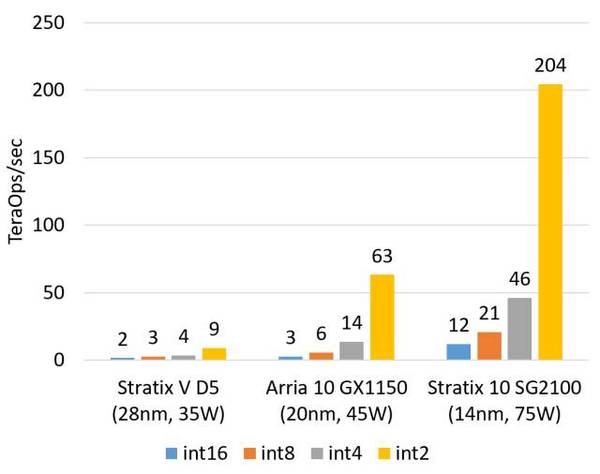

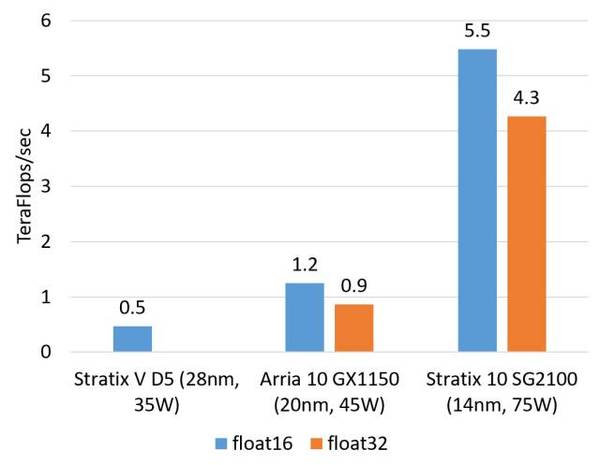

不同体系结构性能和灵活性的比较 FPGA 为什么快?「都是同行衬托得好」。CPU、GPU 都属于冯·诺依曼结构,指令译码执行、共享内存。FPGA 之所以比 CPU 甚至 GPU 能效高,本质上是无指令、无需共享内存的体系结构带来的福利。 冯氏结构中,由于执行单元(如 CPU 核)可能执行任意指令,就需要有指令存储器、译码器、各种指令的运算器、分支跳转处理逻辑。由于指令流的控制逻辑复杂,不可能有太多条独立的指令流,因此 GPU 使用 SIMD(单指令流多数据流)来让多个执行单元以同样的步调处理不同的数据,CPU 也支持 SIMD 指令。而 FPGA 每个逻辑单元的功能在重编程(烧写)时就已经确定,不需要指令。 冯氏结构中使用内存有两种作用。一是保存状态,二是在执行单元间通信。由于内存是共享的,就需要做访问仲裁;为了利用访问局部性,每个执行单元有一个私有的缓存,这就要维持执行部件间缓存的一致性。对于保存状态的需求,FPGA中的寄存器和片上内存(BRAM)是属于各自的控制逻辑的,无需不必要的仲裁和缓存。对于通信的需求,FPGA每个逻辑单元与周围逻辑单元的连接在重编程(烧写)时就已经确定,并不需要通过共享内存来通信。 说了这么多三千英尺高度的话,FPGA 实际的表现如何呢?我们分别来看计算密集型任务和通信密集型任务。 计算密集型任务的例子包括矩阵运算、图像处理、机器学习、压缩、非对称加密、必应搜索的排序等。这类任务一般是 CPU 把任务卸载(offload)给 FPGA 去执行。对这类任务,目前我们正在用的 Altera(似乎应该叫 Intel 了,我还是习惯叫 Altera……)Stratix V FPGA 的整数乘法运算性能与 20 核的 CPU 基本相当,浮点乘法运算性能与 8 核的 CPU 基本相当,而比 GPU 低一个数量级。我们即将用上的下一代 FPGA,Stratix 10,将配备更多的乘法器和硬件浮点运算部件,从而理论上可达到与现在的顶级 GPU 计算卡旗鼓相当的计算能力。

FPGA 的整数乘法运算能力(估计)

FPGA 的浮点乘法运算能力(估计) 在数据中心,FPGA 相比 GPU 的核心优势在于延迟。像必应搜索排序这样的任务,要尽可能快地返回搜索结果,就需要尽可能降低每一步的延迟。如果使用 GPU 来加速,要想充分利用 GPU 的计算能力,batch size 就不能太小,延迟将高达毫秒量级。使用 FPGA 来加速的话,只需要微秒级的 PCIe 延迟(我们现在的 FPGA 是作为一块 PCIe 加速卡)。未来 Intel 推出通过 QPI 连接的 Xeon + FPGA 之后,CPU 和 FPGA 之间的延迟更可以降到 100 纳秒以下,跟访问主存没什么区别了。 (责任编辑:本港台直播) |